ORG447X Series Datasheet Fully Integrated GPS Modules

# Fully Integrated GPS Receiver Engine Module ORG447X Series Data Sheet

All trademarks are properties of their respective owners.

Performance characteristics listed in this document do not constitute a warranty or guarantee of product performance. OriginGPS assumes no liability or responsibility for any claims or damages arising out of the use of this document, or from the use of integrated circuits based on this document.

OriginGPS reserves the right to make changes in its products, specifications and other information at any time without notice. OriginGPS navigation products are not recommended to use in life saving or life sustaining applications.

Document number: 010311For technical questions contact: info@origingps.comwww.origingps.comRevision: B00- 1 -01-03-11

# ORG447X Series Datasheet Fully Integrated GPS Modules

# 1. Introduction

The ORG447X series module is industry's smallest, autonomous, fully featured GPS engine.

The ORG447X series module is miniature multi-channel receiver that continuously tracks all satellites in view and provides accurate positioning data in industry's standard NMEA format.

Internal ARM CPU core and sophisticated firmware keep GPS payload off the host and allow integration in low resources embedded solutions.

Featuring OriginGPS proprietary Noise-Free Zone System (NFZ<sup>™</sup>) technology the ORG447X offers the ultimate in high sensitivity GPS performance in small size.

The ORG447XX series module is complete SiP (System-in-Package) featuring advanced miniature packaging technology and an ultra small footprint designed to commit unique integration features for high volume, low power and cost sensitive applications.

The ORG447X module incorporates new SiRFstarIV<sup>™</sup> GPS processor.

The revolutionary SiRFstarIV<sup>™</sup> architecture is optimized for how people really use location-aware products: often indoors with periods of unobstructed sky view when moving from place to place.

This new architecture can detect changes in context, temperature, and satellite signals to achieve a state of near continuous availability by maintaining and opportunistically updating its internal fine time, frequency, and satellite Ephemeris data while consuming mere microwatts of battery power.

#### **Fully Integrated GPS Modules**

# 2. Description

OriginGPS has researched and enhanced the performance of standard GPS receivers in real-life applications.

Case study of the specifications of key components through involvement in R&D effort of major vendors derived in highest performance in industry's smallest footprint parts available.

These carefully selected key components resulted in higher sensitivity, faster position fix, navigation stability and operation robustness under rapid environmental changes creating hard-to-achieve laboratory performance in heavy-duty environment.

# 2.1.Features

- Stand alone operation

- OriginGPS Noise Free Zone System (NFZ<sup>™</sup>) technology

- Integrated LNA, SAW Filter, TCXO and RTC

- SiRFstarIV<sup>™</sup> GSD4e GPS processor

- L1 frequency, C/A code

- 48 track verification channels

- Navigation sensitivity: -160dBm

- Tracking sensitivity: -163dBm for indoor fixes

- Fast TTFF:

Source Cold Start conditions

- < 1s under Hot Start conditions</pre>

- Multipath mitigation and indoor tracking

- Active Jammer Remover: tracks up to 8 CW interferers and removes jammers up to 80dB-Hz

- SBAS (WAAS, EGNOS, MSAS) support<sup>1</sup>

- Almanac Based Positioning (ABP<sup>™</sup>)<sup>1</sup>

- Client Generated Extended Ephemeris (CGEE<sup>™</sup>) and Server Generated Extended Ephemeris (SGEE<sup>™</sup>) for very fast TTFFs are supported through SiRFInstantFix<sup>™</sup> and SiRFInstantFixII<sup>™</sup>

- Assisted GPS (A-GPS) support

- Automatic and user programmable power saving scenarios: ATP<sup>™</sup>, PTF<sup>™</sup>, APM<sup>™</sup>

- SiRFAware<sup>™</sup> Micro Power Mode (MPM<sup>™</sup>) support<sup>1</sup>

- Low power consumption: <10mW during ATP<sup>™</sup>

- ARM7<sup>®</sup> 109MHz baseband CPU

- Smart sensor I<sup>2</sup>C master interface<sup>1</sup>

- Selectable UART, SPI or I<sup>2</sup>C host interface

- Programmable communication protocol and message rate

- Selectable NMEA or OSP (SiRF Binary) communication standards

- Single voltage supply: 1.8V

- DC blocked 50Ω antenna input

- Ultra small footprint: 7mm x 7mm

- Surface Mount Device (SMD)

- Optimized for automatic assembly and reflow equipment

- Industrial operating temperature range: -40<sup>0</sup> to 85<sup>0</sup>C

- Pb-Free RoHS compliant

Note: 1. Not available in modules with Standard firmware

# 2.2.Architecture

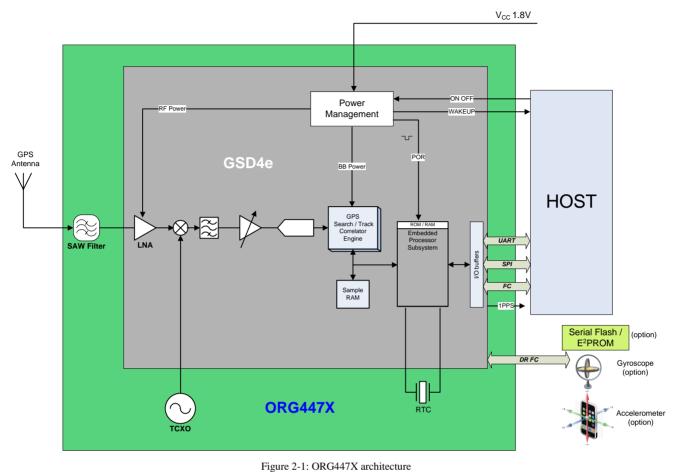

#### Tigure 2-1. OKO++

Band-pass SAW filter

Band-pass SAW filter eliminates inter-modulated out-of-band signals that may corrupt GPS receiver performance.

#### LNA (Low Noise Amplifier)

The integrated LNA amplifies the GPS signal to meet RF down converter input threshold. Noise figure optimized design was implemented to provide maximum sensitivity.

#### TCXO (Temperature Compensated Crystal Oscillator)

This highly stable 16.369 MHz oscillator controls the down conversion process in RF block. Highest characteristics of this component are key factors in fast TTFF.

#### RTC (Real Time Clock) crystal

This miniature component with very tight specifications is necessary for maintaining Hot start and Warm start capabilities.

#### RF shield

RF enclosure avoids external interference to compromise sensitive circuitry inside the receiver. RF shield is also blocks module's internal emissions from being transmitted.

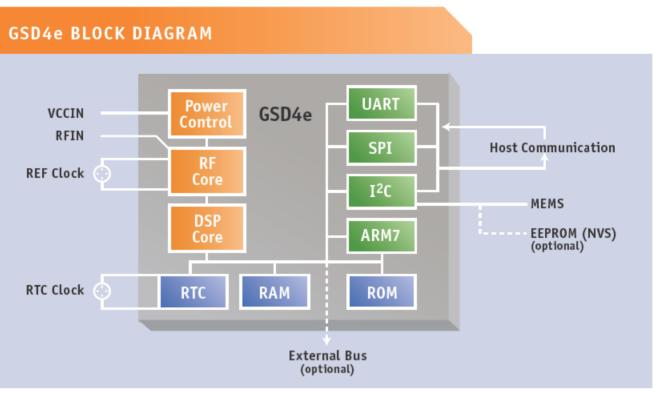

GSD4e IC

Figure 2-2: GSD4e functional block diagram

SiRFstarIV<sup>™</sup> GSD4e GPS processor includes the following units:

- GPS RF core incorporating LNA, down converter, fractional-N synthesizer and ADC block with selectable 2 and 4-bit quantization

- GPS DSP core incorporating more than twice the clock speed and more than double the RAM capacity relative to predecessor market benchmarking SiRFStarIII<sup>™</sup> DSP core

- ARM7<sup>®</sup> microprocessor system incorporating 109MHz CPU and interrupt controller

- ROM block as code storage for PVT applications

- RAM block for data cache

- RTC block

- UART block

- SPI block

- I<sup>2</sup>C block

- Power control block for internal voltage domains management

#### **Fully Integrated GPS Modules**

### **2.3.Applications**

ORG447X series GPS receiver modules have been designed to address new markets where ultra small size and high performance does commit to traditional GPS modules demand for standalone operation, high level of integration, power consumption and design flexibility.

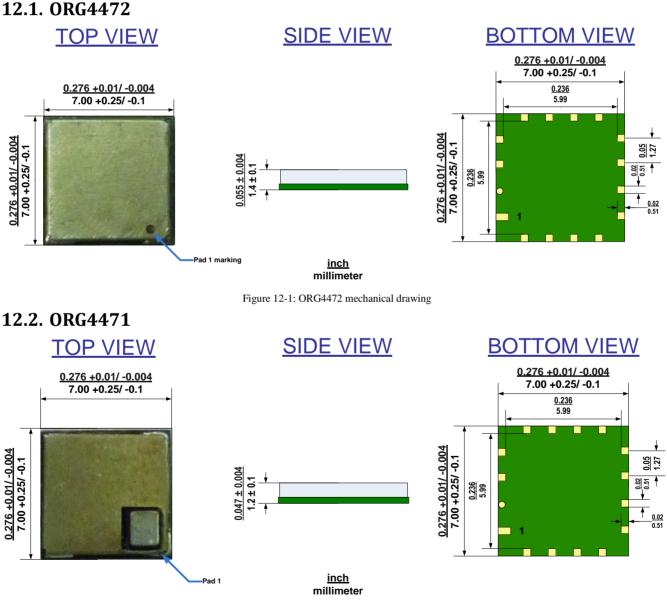

#### ORG4472

The ORG4472 is standard version of the ORG447X series GPS antenna modules.

The ORG4472 is ideal for standard positioning and navigation applications including indoor tracking:

- Personal locators

- Pet collars

- People and animal tracking systems

- Asset tracking SKU systems

- Sports and recreation accessories

- Handheld consumer navigation and multifunction devices

- Rescue and emergency systems

- Precise timing devices

- Micro robots and micro UAVs

- Automatic Vehicle Location

- Automotive navigation

- Workforce management

- Railway monitoring

- GIS and mapping

- Civil engineering

- Agriculture automation

- Maritime navigation

- Electronic Toll Collection

- Automotive security systems

- Data loggers

- Weather balloons

- WiMAX base stations, Femto and Pico cells

- Industrial sensor platforms

- Location Based Services

- Scientific applications

#### <u>ORG4471</u>

The ORG4471 is ideal for highly embedded portable electronics applications with height limitations.

- Mobile handsets

- GPS watches

- Digital still cameras

- Mobile game consoles

- Homeland security applications

#### **Fully Integrated GPS Modules**

# 3. Electrical Specifications

# **3.1.Absolute Maximum Ratings**

Absolute Maximum Ratings are stress ratings only.

Stresses exceeding Absolute Maximum Ratings may damage the device.

| Parameter               | Symbol                             | Min                  | Max  | Units |                |

|-------------------------|------------------------------------|----------------------|------|-------|----------------|

| Power Supply Voltage    |                                    | V <sub>cc</sub>      | -    | 2.2   | V              |

| RF Input Voltage        |                                    | $V_{RF_{IN}}$        | -50  | 50    | V              |

| Power Dissipation       |                                    | PD                   | -    | 200   | mW             |

| I/O Voltage             |                                    | V <sub>IO</sub>      | -0.3 | 3.6   | V              |

| I/O Source/Sink Current |                                    |                      | -10  | +10   | mA             |

| PE Input Dowor          | f <sub>IN</sub> = 1560MHz÷1590MHz  | <b>D</b>             | -    | 10    | dBm            |

| RF Input Power          | f <sub>IN</sub> <1560MHz, >1590MHz | - P <sub>RF_IN</sub> | -    | +15   | dBm            |

| CCD Dating              | I/O pads                           | V <sub>IO(ESD)</sub> | -2   | +2    | kV             |

| ESD Rating              | V <sub>RF(ESD)</sub>               | -1                   | +1   | kV    |                |

| Storage temperature     |                                    |                      | -55  | +125  | <sup>0</sup> C |

| Lead temperature (10    | sec. @ 1mm from case)              | T <sub>LEAD</sub>    | -    | +260  | <sup>0</sup> C |

Table 3-1: Absolute maximum ratings

#### **Fully Integrated GPS Modules**

# **3.2. Recommended Operating Conditions**

Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

| Parameter                          | Symbol                 | Mode / Pad            | Test Conditions               | Min                 | Тур                  | Max  | Units          |

|------------------------------------|------------------------|-----------------------|-------------------------------|---------------------|----------------------|------|----------------|

| Power supply voltage               | V <sub>CC</sub>        |                       |                               | 1.71                | 1.80                 | 1.89 | V              |

|                                    |                        | Acquisition           |                               |                     | 37                   | 47   | mA             |

|                                    |                        | Tracking              |                               | 5                   |                      | 37   | mA             |

| Power Supply Current               | 1                      | CPU only <sup>1</sup> | -130dBm (Outdoor)             |                     | 14                   |      | mA             |

|                                    | I <sub>CC</sub>        | MPM <sup>™</sup> 2    | $T_{AMB} = 25^{0}C$           |                     | 0.5                  |      | mA             |

|                                    |                        | Standby <sup>1</sup>  |                               |                     | 90                   |      | μA             |

|                                    |                        | Hibernate             |                               |                     | 20                   | 25   | μA             |

| Input Voltage Low State            | V <sub>IL</sub>        |                       |                               |                     |                      | 0.45 | V              |

| Input Voltage High State           | V <sub>IH</sub>        |                       |                               | $0.70 \cdot V_{CC}$ |                      | 3.6  | V              |

| Output Voltage Low State           | V <sub>OL</sub>        |                       | I <sub>OL</sub> = 2mA         |                     |                      | 0.40 | V              |

| Output Voltage High State          | V <sub>OH</sub>        |                       | I <sub>OH</sub> = -4mA        | $0.75 \cdot V_{CC}$ | V <sub>CC</sub> -0.1 |      | V              |

| Input Capacitance                  | C <sub>IN</sub>        | GPIO                  |                               |                     | 4                    | 10   | рF             |

| Internal Pull-up Resistor          | R <sub>PU</sub>        |                       |                               | 50                  | 86                   | 157  | kΩ             |

| Internal Pull-down Resistor        | R <sub>PD</sub>        |                       |                               | 51                  | 91                   | 180  | kΩ             |

| Input Leakage Current              | I <sub>IN(leak)</sub>  |                       | V <sub>IN</sub> = 1.8V or 0V  | -10                 |                      | +10  | μA             |

| Output Leakage Current             | I <sub>OUT(leak)</sub> |                       | V <sub>OUT</sub> = 1.8V or 0V | -10                 |                      | +10  | μΑ             |

| Input Impedance                    | Z <sub>IN</sub>        | DElegent              |                               |                     | 50                   |      | Ω              |

| Input Return Loss                  | RL <sub>IN</sub>       | RF Input              | f <sub>0</sub> = 1575.5 MHz   |                     | -8                   |      | dB             |

| Operating Temperature <sup>3</sup> | T <sub>AMB</sub>       |                       |                               | -40                 | +25                  | +85  | <sup>0</sup> C |

| Relative Humidity                  | RH                     |                       | Oper. Temp.                   | 5                   |                      | 95   | %              |

Table 3-2: Operating conditions

Notes:

1. Transitional states of ATP<sup>™</sup> low power mode 2. Average current during SiRFAware<sup>™</sup> Micro Power Mode 3. Operation below -30<sup>0</sup>C to -40<sup>0</sup>C is accepted, but TTFF may increase

Document number: 010311 For technical questions contact: info@origingps.com **Revision: B00** 01-03-11

# 4. Performance

# **4.1.Acquisition Times**

TTFF (Time To First Fix) – is the period of time from GPS power-up till position estimation.

#### **Hot Start**

A hot start results from software reset after a period of continuous navigation or a return from a short idle period that was preceded by a period of continuous navigation. In this state, all of the critical data (position, velocity, time, and satellite ephemeris) is valid to the specified accuracy and available in SRAM.

#### Warm Start

A warm start typically results from user-supplied position and time initialization data or continuous RTC operation with an accurate last known position available in memory. In this state, position and time data are present and valid, but ephemeris data validity has expired.

#### **Cold Start**

A cold start acquisition results when either position or time data is unknown. Almanac information is used to identify previously healthy satellites.

#### **Aided Start**

Aiding is a method of effectively reducing the TTFF by making every start Hot or Warm.

|                          | TTFF  | <b>Test Condition</b> | Signal Level |

|--------------------------|-------|-----------------------|--------------|

| Hot Start                | < 1s  | Outdoor               | -130 dBm     |

| Aided Start <sup>1</sup> | < 10s | Outdoor               | -130 dBm     |

| Warm Start               | < 32s | Outdoor               | -130 dBm     |

| Cold Start               | < 35s | Outdoor               | -130 dBm     |

| Signal Reacquisition     | < 1s  | Outdoor               | -130 dBm     |

Table 4-1: Acquisition times (typical)

# 4.2.Sensitivity

|                    | Signal Level |

|--------------------|--------------|

| Tracking           | -163 dBm     |

| Navigation         | -161 dBm     |

| Aided <sup>1</sup> | -156 dBm     |

| Cold Start         | -148 dBm     |

Table 4-2: Sensitivity

#### Note:

1.Host-assisted device by SGEE<sup>™</sup> or self-assisted by CGEE<sup>™</sup> or Ephemeris push

# 4.3. Power Consumption

| Operation Mode | Power    |

|----------------|----------|

| Acquisition    | 67mW     |

| Tracking       | 9 - 67mW |

| Hibernate      | 36µW     |

Table 4-4: Power consumption (typical)

# 4.4. Accuracy

|          |            | Method      | Accurac | Units | Test Conditions                  | Signal Level |

|----------|------------|-------------|---------|-------|----------------------------------|--------------|

|          |            |             | < 2.5   | m     | Outdoor, 24-hr. static           | -130 dBm     |

|          | Horizontal | CEP (50%)   | < 2     | m     | Outdoor, 24-hr. static , SBAS on | -130 dBm     |

|          | Horizontal |             | < 5     | m     | Outdoor, 24-hr. static           | -130 dBm     |

| Desition |            | 2dRMS (95%) | < 4     | m     | Outdoor, 24-hr. static , SBAS on | -130 dBm     |

| Position |            |             | < 4     | m     | Outdoor, 24-hr. static           | -130 dBm     |

|          | Vertical   | VEP (50%)   | < 3     | m     | Outdoor, 24-hr. static , SBAS on | -130 dBm     |

|          | Vertical   |             | < 7.5   | m     | Outdoor, 24-hr. static           | -130 dBm     |

|          |            | 2dRMS (95%) | < 6     | m     | Outdoor, 24-hr. static , SBAS on | -130 dBm     |

| Velocity | Horizontal | 50%         | < 0.01  | m/s   | Outdoor, 30 m/s                  | -130 dBm     |

| Heading  |            | 50%         | < 0.01  | 0     | Outdoor, 30 m/s                  | -130 dBm     |

| Time     |            | 1 PPS       | < 1     | μs    | Outdoor                          | -130 dBm     |

Table 4-5: Accuracy

# 4.5. Dynamic Constrains<sup>1</sup>

| Velocity <     | 515 m/s 1,000 knot |            |  |

|----------------|--------------------|------------|--|

| Acceleration < | 4g                 |            |  |

| Altitude <     | 18,288 m           | 60,000 ft. |  |

Table 4-6: Dynamic constrains

### **Fully Integrated GPS Modules**

# 5. Power Management

# **5.1.** Power states

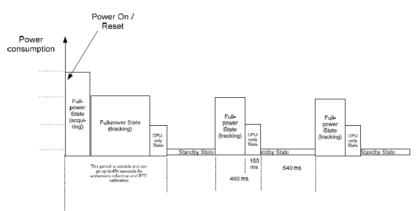

#### Full Power state (Acquisition/Tracking)

The module stays in full power until a position solution is made and estimated to be reliable. During the acquisition, processing is more intense than during tracking, thus consuming more power.

#### CPU Only state

This is the state when the RF and DSP sections are partially powered off.

The state is entered when the satellites measurements have been acquired but the navigation solution still needs to be computed.

#### Standby state

This is the state when the RF and DSP sections are completely powered off and baseband clock is stopped.

#### Hibernate state

In this state the RF, DSP and baseband sections are completely powered off leaving only the RTC and Battery-Backed RAM running.

The module will perform Hot Start if held in Hibernate state less than 2 hours after valid position solution was acquired.

# 5.2. Power saving modes

The ORG447X series has three power management modes available in modules with Basic and Standard firmware – ATP<sup>™</sup>, APM<sup>™</sup> and PTF<sup>™</sup> and additional SiRFAware<sup>™</sup> Micro Power Mode (MPM<sup>™</sup>) available in modules with Premium firmware which are controlled by internal state machine. These modes provide different levels of power saving with different degradation level of position accuracy.

#### Fully Integrated GPS Modules

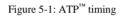

# Adaptive Trickle Power (ATP<sup>™</sup>)

Adaptive Trickle Power (ATP<sup>™</sup>) is best suited for applications that require navigation solutions at a fixed rate as well as low power consumption and an ability to track weak signals.

This power saving mode provides the most accurate positioning.  $\prod_{i=1}^{M}$

In ATP<sup>™</sup> mode the ORG447X series module is intelligently cycled between Full Power, CPU Only and Standby states to optimize low power operation.

# Push-To-Fix (PTF<sup>™</sup>)

Push-To-Fix (PTF<sup>™</sup>) is best suited for applications that require infrequent navigation solutions, optimizing battery life time.

In PTF<sup>™</sup> mode the ORG447X series module is mostly in Hibernate state, waked up for Ephemeris and Almanac refresh in fixed periods of time.

The PTF<sup>™</sup> period is 30 minutes by default but can be anywhere between 10 seconds and 2 hours. When the PTF<sup>™</sup> mode is enabled the receiver will stay in Full Power state until the good navigation solution is computed.

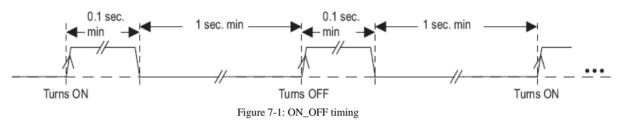

When the application needs a position report it can toggle the ON\_OFF pad to wake up the module. In this case, a new PTF<sup>™</sup> cycle with default settings begins.

Figure 5-2: PTF<sup>™</sup> timing

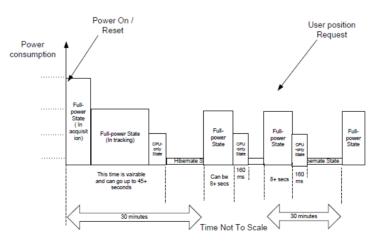

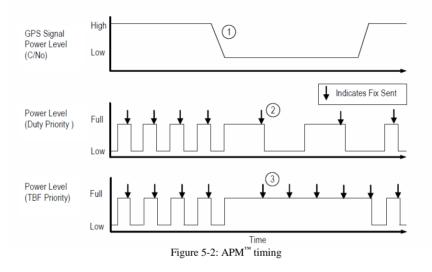

# Advanced Power Management (APM<sup>™</sup>)

Advanced Power Management (APM<sup>™</sup>) is designed to give the user more options to configure the power management. The APM<sup>™</sup> mode allows power savings while ensuring that the Quality of the Solution (QoS) in maintained when signals level drop.

In addition to setting the position report interval, a QoS specification is available that sets allowable error estimates and selects priorities between position report interval and more power saving. The user may select between Duty Cycle Priority for more power saving and TBF (Time Between Fixes) Priority with defined or undefined maximum horizontal error.

TBF range is from 10 to 180 sec. between fixes, Power Duty Cycle range is between 5 to 100%. Maximum position error is configurable between 1 to 160m.

The number of  $APM^{T}$  fixes is configurable up to 255 or set to continuous.

In APM<sup>™</sup> mode the module is intelligently cycled between Full Power and Hibernate states.

1. GPS signal level drops (e.g user walks indoors)

2. Lower signal results in longer ON time. To maintain Duty Cucle, OFF time is increased.

3. Lower signal means missed fix. To maintain future TBFs, the module goes info Full Power state until signal levels improve.

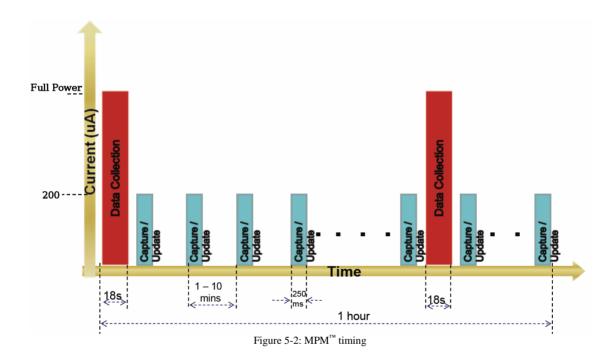

# SiRFAware<sup>™</sup> Micro Power Mode (MPM<sup>™</sup>)<sup>1</sup>

With SiRFAware<sup>™</sup>, the receiver determines how much signal processing to do and how often to do it, so that the receiver is always able to do a fast hot start (TTFF < 2 s) on demand. In this mode the receiver is configured to wake up (typically twice an hour) for 18-24 sec. to collect new Ephemeris data. Ephemeris Data Collection operation consumes the current equal to Full Power state.

Additionally, the module will wake up once every 1 to 10 min. for 250ms to update internal navigation state and GPS time calibration. Capture/Update operation consumes about 200µA. Rest of the time the receiver remains in Hibernate state.

The host sends ON\_OFF interrupt to wake up the module.

After valid fix is available, the host can turn the module back into MPM<sup>™</sup> by re-sending the configuration message.

Average current consumption over long period during  $MPM^{\text{T}}$  is about 0.5mA.

#### **Fully Integrated GPS Modules**

# 6. Extended Features

# 6.1.Almanac Based Positioning (ABP<sup>™</sup>)<sup>1</sup>

With  $ABP^{M}$  mode enabled, the user can get shorter Cold Start TTFF as a tradeoff with the position error.

When no sufficient Ephemeris data is available to calculate an accurate solution, a coarse solution will be provided where the position is calculated based on one or more of the SVs having their states derived from Almanac data.

Almanac data for  $ABP^{M}$  purposes may be stored factory set, broadcasted or pushed.

# **6.2. Active Jammer Remover**

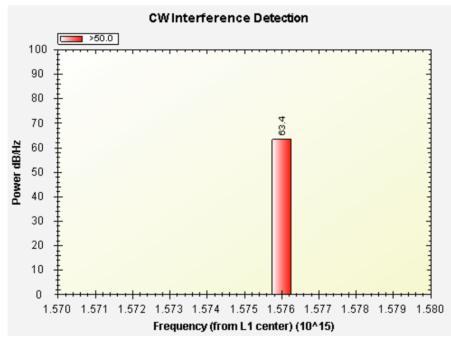

Jamming Remover is an embedded DSP block that detects, tracks and removes up to 8 Continuous Wave (CW) type signals of up to 80dB-Hz each. Jamming Remover is effective only against continuous narrow band interference signals and covers GPS L1 frequency ±4MHz.

Figure 6-1: Active Jammer Detection frequency plot

# 6.3. Client Generated Extended Ephemeris (CGEE<sup>™</sup>)

The CGEE<sup>™</sup> feature allows shorter TTFF by providing predicted (synthetic) ephemeris files created within a lost host system from previously received broadcast Ephemeris.

The prediction process requires good receipt of broadcast Ephemeris data for all satellites.

EE files created this way are good for up to 3 days and then expire.

The CGEE<sup>™</sup> feature requires avoidance of power supply removal.

CGEE<sup>™</sup> data files are stored on internal or external EEPROM or Serial Flash and managed by the receiver or storage and management is done by host.

Note:

1. Not available in modules with Standard firmware

# **Fully Integrated GPS Modules**

# 7. Interface

# 7.1.Pad Assignment

| Pad | Name            | Pad Description                           | Direction | Full Power | Hibernate | Notes                   |

|-----|-----------------|-------------------------------------------|-----------|------------|-----------|-------------------------|

| 1   | GND             | System Ground                             | Power     |            |           |                         |

| 2   | RF_IN           | Antenna Signal Input                      | Input     |            |           |                         |

| 3   | GND             | System Ground                             | Power     |            |           |                         |

| 4   | WAKEUP          | Power Status                              | Output    | High       | Low       |                         |

| 5   | nRESET          | Asynchronous Reset                        | Input     | High       | High      | Internal pull-up        |

| 6   | nCTS            | UART CTS / SPI CLK                        | Bi-dir.   | Low        | Low       | Internal pull-down      |

| 7   | nRTS            | UART RTS / SPI nCS                        | Bi-dir.   | High       | High      | Internal pull-up        |

| 8   | RX              | UART RX / SPI MOSI / I <sup>2</sup> C SDA | Bi-dir.   | High       | Hi-Z      |                         |

| 9   | ON_OFF          | Power State Control                       | Input     | Low        | Low       | Schmitt-triggered input |

| 10  | 1PPS            | UTC Time Mark                             | Output    | Low        | Low       |                         |

| 11  | TX              | UART TX / SPI MISO / I <sup>2</sup> C SCL | Bi-dir.   | Low        | Hi-Z      |                         |

| 12  | V <sub>CC</sub> | System Power                              | Power     |            |           |                         |

| 13  | RTC             | Future use                                |           |            |           | Do not connect          |

| 14  | GND             | System Ground                             | Power     |            |           |                         |

| 15  | DR_SDA          | DR I <sup>2</sup> C Serial Data           | Output    |            | Hi-Z      |                         |

| 16  | DR_SCL          | DR I <sup>2</sup> C Serial Clock          | Bi-dir.   |            | Hi-Z      |                         |

Table 7-1: Pin-out

### **Fully Integrated GPS Modules**

# 7.2.Connectivity

#### 7.2.1. Power

#### Power supply

The ORG447X series module requires only one power supply V<sub>CC</sub> of 1.8V DC. It is recommended to keep the power supply on all the time in order to maintain the nonvolatile RTC and RAM active for fastest possible TTFF. When powering the ORG447X module from switching mode (DC-DC) power supply carefully follow manufacturer's application notes and apply filtering to minimize ripple. Voltage ripple below 300mV<sub>PP</sub> allowed for frequency under 10KHz. Voltage ripple below 100mV<sub>PP</sub> allowed for frequency between 10KHz and 100KHz. Voltage ripple below 50mV<sub>PP</sub> allowed for frequency between 100KHz and 1MHz. Voltage ripple below 10mV<sub>PP</sub> allowed for frequency above 1MHz. Higher voltage ripple may compromise the ORG447X module performance. When the V<sub>CC</sub> is powered off settings are reset to factory default and the receiver performs Cold Start on next power up. Power supply current varies according to the processor load and satellite acquisition. Typical I<sub>CC</sub> current is 40mA during acquisition. Peak I<sub>CC</sub> current is 55mA.

Typical  $I_{CC}$  current in Hibernate state is  $20\mu A.$

#### <u>Ground</u>

All Ground pads should be connected to the main Ground plane with shortest possible traces or vias.

#### **Fully Integrated GPS Modules**

#### 7.2.2. Host Control Interface

#### ON OFF control input

The ON\_OFF control input can be used to switch the receiver between Normal or Hibernate states and also to generate interrupt in PTF<sup>™</sup> mode.

The ON\_OFF interrupt is generated by a low-high-low toggle, which should be longer than  $62\mu s$  and less than 1s (100ms pulse length recommended).

ON\_OFF interrupts with less than 1 sec intervals are not recommended.

Multiple switch bounce pulses are recommended to be filtered out.

ON\_OFF input is 3.6V tolerant. Pull-down resistor of  $33k\Omega$ - $82k\Omega$  is recommended. Must be connected to host.

#### nRESET input

The Power-on-Reset (POR) is generated internally in the ORG447X module.

Additionally, manual reset option is available through nRESET pad.

Resetting the module clears the RTC block and configuration settings become default.

nRESET pad is active low and has internal pull-up resistor of  $86k\Omega$  (typ.).

nRESET signal should be applied for at least 1µs.

Do not drive nRESET input high.

Do not connect if not in use.

#### WAKEUP output

The WAKEUP pad is an output from the ORG447X used to flag for power mode. A low on this output indicates that the module is in one of its low-power states -Hibernate or Standby.

A high on this output indicates that the module is in Full Power operating mode.

WAKEUP output can be used to control enable of auxiliary devices, like level translator, active antenna bias, or to flag for high current demand from power supply.

Wakeup output is LVCMOS 1.8V compatible.

#### 1PPS output

The pulse-per-second (PPS) output provides a pulse signal for timing purposes. Pulse length (high state) is 200ms, and less than 1µs synchronized to full UTC second. The UTC time message is generated and put into output FIFO 300ms after PPS rising edge. The exact time between the PPS and UTC time message delivery depends on message rate, message queue and communication baud rate. 1PPS output is LVCMOS 1.8V compatible. Do not connect if not in use.

#### **Fully Integrated GPS Modules**

#### 7.2.3. Host Data Interface

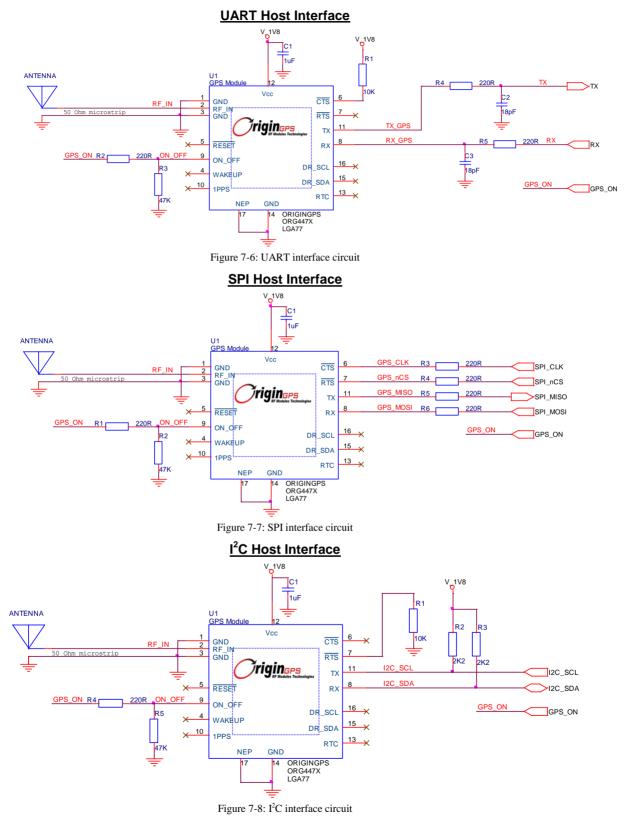

The ORG447X has 3 types of interface ports to connect to host: UART, SPI and  $I^2C$ . All ports are multiplexed on a shared set of pads.

At system reset, the host port interface lines are disabled, so no conflict occurs.

Configuration straps on nCTS and nRTS are read by the module firmware during startup and define port type. Use  $10k\Omega$  resistor for external strap.

| Port Type        | nCTS               | nRTS               |

|------------------|--------------------|--------------------|

| UART             | External pull-up   | Internal pull-up   |

| SPI (default)    | Internal pull-down | Internal pull-up   |

| l <sup>2</sup> C | Internal pull-down | External pull-down |

Table 7-2: ORG447X host interface selection

#### <u>UART</u>

The module has a 4-wire UART port:

- TX used for GPS data reports.

- RX used for receiver control.

- nCTS and nRTS are optionally used for hardware flow control.

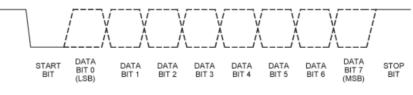

The default protocol is NMEA@4,800bps 8-N-1 (8 data bits, No parity, 1 stop bit).

The configuration for baud rates and respective protocols can be changed by commands via NMEA or OSP (SiRF Binary) protocols. Baud rates are configurable from 900bps to 1.8Mbps.

| Baud Rate (bps) | Error (%) | Baud Rate (bps) | Error (%) | Baud Rate (bps) | Error (% |

|-----------------|-----------|-----------------|-----------|-----------------|----------|

| 900             | 0.00      | 14400           | 0.62      | 230400          | 1.04     |

| 1200            | 0.00      | 19200           | 0.00      | 307200          | 0.01     |

| 1800            | 0.00      | 28800           | 0.00      | 460800          | 0.60     |

| 2400            | 0.00      | 38400           | 0.07      | 614400          | 1.10     |

| 3600            | 0.00      | 57600           | 0.64      | 921600          | 2.30     |

| 4800            | 0.06      | 76800           | 0.01      | 1228800         | 0.07     |

| 7200            | 0.00      | 115200          | 0.24      | 1843200         | 0.86     |

| 9600            | 0.00      | 153600          | 0.03      |                 |          |

Table 7-3: ORG447X UART baud rate tolerance

#### Outputs are LVCMOS 1.8V compatible. Inputs are 3.6V tolerant.

Figure 7-2: UART integrity

(%)

#### **Fully Integrated GPS Modules**

#### <u>SPI</u>

The SPI (Serial to Peripheral Interface) is a master/slave synchronous serial bus that consists of 4 signals:

- Serial Clock (SCK) from master to slave.

- Serial Data Out (also called Master Out Slave In or MOSI) from master.

- Serial Data In (also called Master In Slave Out or MISO) from slave.

- Chip Select (CS) from master.

The host interface SPI of the ORG447X module is a slave mode SPI.

The four SPI pads are RX (MOSI), TX (MISO), nRTS(nCS) and nCTS(SCK).

Output is LVCMOS 1.8V compatible. Inputs are 3.6V tolerant.

The host interface SPI features are:

- TX and RX each have independent 1024 byte FIFO buffers.

- RX and TX have independent, software specified two byte idle patterns of 0xA7 0xB4.

- TX FIFO is disabled when empty and transmits its idle pattern until re-enabled.

- RX FIFO detects a software specified number of idle pattern repeats and then disables FIFO input until the idle pattern is broken.

- FIFO buffers can generate an interrupt at any fill level.

- SPI detects synchronization errors and can be reset by software.

- Supports a maximum clock of 6.8MHz.

- Default GPS data output format is NMEA standard.

#### Figure 7-3: SPI timing

| Symbol           | Parameter           | Min | Max | Units            |

|------------------|---------------------|-----|-----|------------------|

| t <sub>clk</sub> | SCK Time Period     | 140 |     | ns               |

| t <sub>css</sub> | nCS Setup Time      | 0.5 | 1   | t <sub>clk</sub> |

| t <sub>cs</sub>  | nCS High Time       | 1   |     | t <sub>clk</sub> |

| t <sub>wн</sub>  | SCK High Time       | 0.5 |     | t <sub>clk</sub> |

| t <sub>wL</sub>  | SCK Low Time        | 0.5 |     | t <sub>clk</sub> |

| t <sub>csH</sub> | nCS Hold Time       | 0.5 | 1   | t <sub>clk</sub> |

| t <sub>su</sub>  | Data In Setup Time  | 0.5 |     | t <sub>clk</sub> |

| t <sub>H</sub>   | Data In Hold Time   | 0.5 |     | t <sub>clk</sub> |

| t <sub>v</sub>   | Output Valid        | 0.5 |     | t <sub>clk</sub> |

| t <sub>HO</sub>  | Output Hold Time    | 0.5 |     | t <sub>clk</sub> |

| t <sub>DIS</sub> | Output Disable Time |     | 0.5 | t <sub>clk</sub> |

Document number: 010311 For technical questions contact: info@origingps.com Revision: B00 01-03-11

#### **Fully Integrated GPS Modules**

#### **Operation:**

The SPI performs bit-by-bit transmitting and receiving at the same time whenever nCS is asserted and SCK is active. In order to communicate properly with SPI device, the protocol must be agreed – specifically- SPI mode and an idle byte pattern.

Among 4 SPI modes of the clock polarity (CPOL) and clock phase (CPHA) only SPI Mode 1 <CPOL="0", CPHA ="1"> has been tested:

• At CPOL="0" the base value of the clock is zero.

• For CPHA="1", data are read on the clock's falling edge and data are changed on a rising edge. On power up, the first message to come out of the module is the "OK\_TO\_SEND" message. It takes about 20ms from power up for the module SPI drivers to get initialized.

The slave has no way of forcing data to the master to indicate it is ready for transmission - the master must poll the client periodically.

Since the specified idle 2-byte pattern for both receive and transmit is 0xA7 0xB4, the master can transmit this idle pattern into the slave repeatedly. If the master receives idle patterns back from the slave, it indicates that the slave currently has nothing to transmit but is ready to communicate.

On the module receive side, the host is expected to transmit idle pattern when it is querying the module's transmit buffer. In this way, the volume of discarded bytes is kept nearly as low as in the UART implementation because the module hardware does not place most idle pattern bytes in its RX FIFO. Most messaging can be serviced with polling. The FIFO thresholds are placed to detect large messages requiring interrupt-driven servicing.

On the module transmit side the intent is to fill the FIFO only when it is disabled and empty. In this condition, the module's SPI driver software loads as many queued messages as can completely fit in the FIFO. Then the FIFO is enabled.

The host is required to poll messages until idle pattern bytes are detected.

At this point the module's FIFO is empty and disabled, allowing the ORG447X SPI driver to again respond to an empty FIFO interrupt and load the FIFO with any messages in queue. <u>Notes:</u>

For SPI communication, read and write operations both require data being sent to the Slave SPI (idle bytes for reads and message data for writes). Any time data is sent to the module via the SPI bus, the Slave SPI of the module will send an equal amount of data back to the host.

These bytes must be buffered either in hardware or software, and it is up to the host to determine if the bytes received may be safely discarded (idle bytes), or should be passed on to the application handling GPS communication. Failure to properly handle data received from the SPI slave can result in corrupted GPS messages.

The external SPI master may send idle bytes and complete messages in a single transmission, provided that idle bytes shall not be inserted inside of a message.

The idle byte pattern and repeat count prevents the problem of messages lost due to normal occurrence of idle byte patterns within message data with high probability.

The external SPI master shall not send partial messages.

All transmissions from the SPI master shall be in multiples of 8 bits.

The external SPI master shall transmit the idle byte pattern when reading the SPI slave's transmit buffer when the master has no message data to transmit.

The SPI slave shall be serviced at a rate that will keep the TX FIFO empty.

# <u>I<sup>2</sup>C</u>

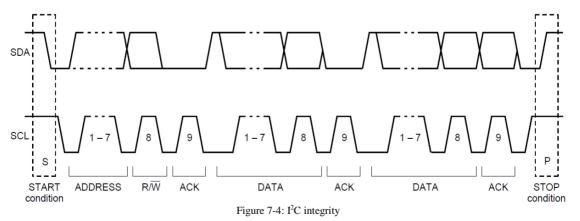

I<sup>2</sup>C is a low- to medium-data-rate master/slave communication bus.

Two wires, serial data (SDA) and serial clock (SCL), carry information between the devices connected to the bus. Each device is recognized by a unique address and can operate as either a transmitter or receiver, depending on the function of the device. In addition to transmitters and receivers, devices can also be considered as masters or slaves when performing data transfers. A master is the device which initiates a data transfer on the bus. At that time, any device addressed is considered a slave.

The physical layer of I<sup>2</sup>C bus is a simple handshaking protocol that relies upon open collector outputs on the bus devices and the device driving or releasing the bus lines, so a pull-up resistor is needed on each wire of the bus.

I<sup>2</sup>C bus is a true multi-master bus including collision detection and arbitration to prevent data corruption if two or more masters simultaneously initiate data transfer

Serial 8-bit oriented bi-directional data transfers can be made at up to 100kbps in the Standardmode of I<sup>2</sup>C bus and up to 400kbps in the Fast-mode.

The Host Interface I<sup>2</sup>C features are:

- Multi-Master I<sup>2</sup>C mode is supported by default.

- Individual transmit and receive FIFO length of 64 bytes.

- The default I<sup>2</sup>C address values are:

- ✤ RX: 0x60

- ✤ TX: 0x62

- Operation speed up to 400kbps.

- SCL and SDA require external pull-up resistors of  $2.2k\Omega$  (typ.).

#### Operation:

The operation of the I<sup>2</sup>C with a master transmit and slave receive mimics a UART operation, where both the module and the host can independently freely transmit.

It is possible to enable the master transmit and slave receive at the same time, as the I<sup>2</sup>C bus allows for contention resolution between the module and the host vying for the bus.

Figure 7-3 shows typical data transfers on the I<sup>2</sup>C bus. The master supplies the clock; it initiates and terminates transactions and the intended slave (based upon the address provided by the master) acknowledges the master by driving or releasing the bus. The slave cannot terminate the transaction but can indicate a desire to by a "NAK" or not-acknowledge.

#### **Fully Integrated GPS Modules**

I<sup>2</sup>C specification defines unique situations as START (S) and STOP (P) conditions. A HIGH to LOW transition on the SDA line while SCL is HIGH indicates a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition. START and STOP conditions are always generated by the master. Every byte put on the SDA line must be 8-bits long.

The number of bytes can be transmitted per transfer is unrestricted.

Each byte is followed by an acknowledge bit.

Data is transferred with the Most Significant Bit (MSB) first. In most cases, data transfer with acknowledge is obligatory. The acknowledge–related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse. Set-up and hold times must be taken into account. All data transfers of I<sup>2</sup>C specification should follow the format.

After the START condition (S), a slave address should be sent first.

This address is 7 bits long followed by an 8-th bit which is a data direction bit (R/nW) – logical 0 indicates a transmission (WRITE), logical 1 indicates a request for data (READ).

After the slave address byte is sent, master can continue its data transfer by writing or reading data byte as defined format. The data transfer is always terminated by a STOP condition generated by the master.

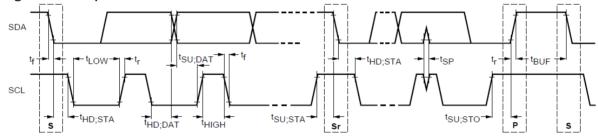

| Figure | 7-5: | $I^2C$ | timing |

|--------|------|--------|--------|

|--------|------|--------|--------|

| Symbol              | Parameter                            | Min | Max                 | Units |

|---------------------|--------------------------------------|-----|---------------------|-------|

| f <sub>SCL</sub>    | SCL frequency                        | 100 | 400                 | kHz   |

| t <sub>HD;STA</sub> | Hold Time for START condition        | 0.6 |                     | μs    |

| t <sub>LOW</sub>    | Low Time of SCL                      | 1.3 |                     | μs    |

| t <sub>HIGH</sub>   | High Time of SCL                     | 0.6 |                     | μs    |

| t <sub>su;sta</sub> | Setup Time for START condition       | 0.6 |                     | μs    |

| t <sub>hd;dat</sub> | Hold Time                            | 0   | 0.9                 | μs    |

| t <sub>su;dat</sub> | Data Setup Time                      | 0.1 |                     | μs    |

| t <sub>r</sub>      | Rise Time of SDA and SCL             |     | 0.3                 | μs    |

| t <sub>f</sub>      | Fall Time of SDA and SCL             |     | 0.3                 | μs    |

| t <sub>su;sto</sub> | Setup Time for STOP condition        | 0.6 |                     | μs    |

| t <sub>BUF</sub>    | Bus Free Time between START and STOP | 1.3 |                     | μs    |

| CL                  | Capacitive Load of SDA and SCL       |     | 400                 | pF    |

| V <sub>nL</sub>     | Noise Margin at the low logic level  |     | $0.1 \cdot V_{CC}$  | V     |

| V <sub>nH</sub>     | Noise Margin at the high logic level |     | 0.2·V <sub>CC</sub> | V     |

Table 7-5: I<sup>2</sup>C timing

#### 7.2.4. Smart Sensors Data Interface

The ORG447X master mode I<sup>2</sup>C interface provides support for dead reckoning (DR) and code patch upload (optional).

The port has 2 pads, DR\_SCL and DR\_SDA, both pins are pseudo open-drain and require pull-up resistors on the external bus.

#### Dead Reckoning (DR) I<sup>2</sup>C Interface

The DR I<sup>2</sup>C interface supports required sensor instruments for dead reckoning applications such as gyros, accelerometers, compasses or other sensors that can operate with an I<sup>2</sup>C bus. The ORG447X module acts as the I<sup>2</sup>C Master and the sensor devices function in Slave mode. This provides a very low latency data pipe for the critical sensor data so that it can be used in the Navigation Library and Kalman filter to enhance navigation performance. The MEMS algorithms perform a sensor data fusion with the GPS signal measurements. GPS measurements can be used to calibrate the MEMS sensors during periods of GPS navigation. The MEMS sensors can augment GPS measurements, and can be more accurate than GPS under degraded GPS signal conditions and certain dynamics.

DR I<sup>2</sup>C interface supports:

- Common sensor formats

- Typical data lengths (command + in/data out) of several bytes

- Standard I<sup>2</sup>C bus maximum data rate 400kbps

- Minimum data rate 100kbps

In current Premium firmware implementation, MEMS sensors integration provides a pseudo "position pinning" feature to prevent position wander and heading instability.

#### Data Storage Support

The DR I<sup>2</sup>C interface is available at boot-up for uploading data from a serial EEPROM. Firmware updates may be provided from time to time to address ROM firmware issues as a method of performance improvement.

The DR I<sup>2</sup>C interface also supports serial flash devices used to store ARM7TDMI patch loads, including optional:

- FIFO support

- ARM7TDMI dedication to I<sup>2</sup>C interface during serial flash read or write

#### 7.2.5. RF input

The antenna input impedance is  $50 \Omega. \label{eq:solution}$  The input is DC blocked.

The module supports active and passive antennas.

In design with passive antenna attention should be paid on antenna layout.

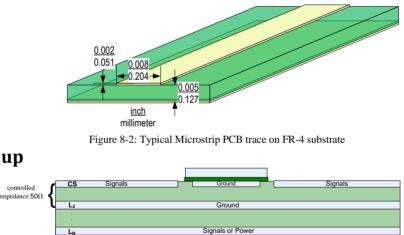

Short trace with controlled impedance of  $50\Omega$  should conduct GPS signal from antenna to RF\_IN pad.

In designs with active antenna DC bias voltage should be applied on RF\_IN through AC blocking inductor. DC bias voltage can be controlled by WAKEUP output through MOSFET or load switch. In designs with active antenna net gain including conductors losses should not exceed 25dB. In designs with external LNA, LNA enable input can be controlled by the ORG447X WAKEUP output.

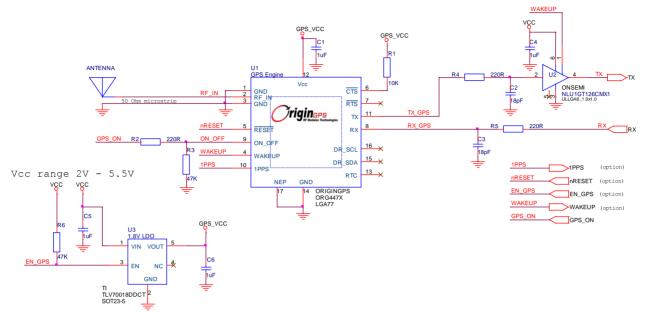

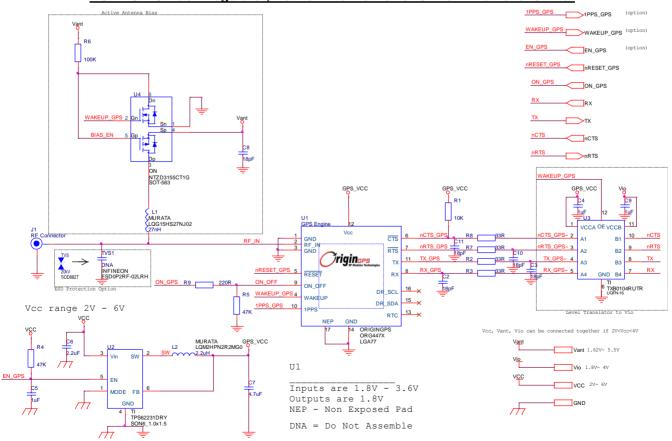

# 7.3. Typical Application Circuit

#### 7.3.1. Minimal Schematic Diagrams

#### 7.3.2. Extended Schematic Diagrams

#### **1.8V LDO Regulator And Level Shifter**

Figure 7-9: UART interface circuit

1.8V DC-DC Buck Regulator, Active Antenna Power Switch And Level Shifter

Figure 7-10: Active Antenna and UART interface circuit

Document number: 010311 For technical questions contact: info@origingps.com www.origingps.com **Revision: B00** - 26 -01-03-11

# 8. PCB Layout

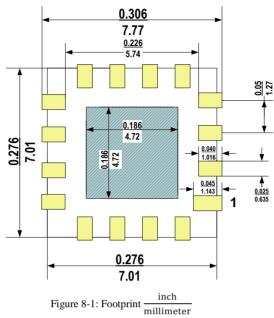

8.1.Footprint

Ground pad at the middle should be connected to main Ground plane by multiple vias. Ground pad at the middle should be solder masked.

Silk print of module's outline is highly recommended for SMT visual inspection.

# 8.2.RF Input trace

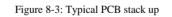

# 8.3.PCB stack up

Groun

# **8.4.Design restrictions**

Keep out of signal or switching power traces and vias under the ORG447X module. Signal traces to/from ORG447X module should have minimum length.

Recommended distance from adjacent active components is 3mm. In case of adjacent high speed components, like CPU or memory, high frequency components, like transmitters, clock resonators or oscillators, metal planes, like LCD or battery enclosures, please contact OriginGPS for more precise, application specific recommendations.

#### **Fully Integrated GPS Modules**

# 9. Operation

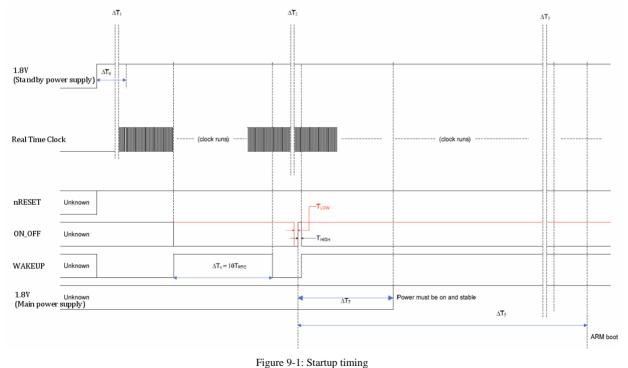

When power is first applied, the ORG447X goes into a Hibernate state while integrated RTC starts and internal FSM sequences though to "Ready-to-Start" state.

The host is not required to control external master nRESET since module's internal reset circuitry handles detection of application of power.

While in "Ready-to-Start" state, the module awaits a pulse to the ON\_OFF input.

Since integrated RTC startup times are variable, detection of when the ORG447X is ready to accept an ON\_OFF pulse requires the host to either wait for a fixed interval, to monitor a pulse on module WAKEUP output that indicates FSM "Ready-to-Start"

Another option is to assert a pulse on the ON\_OFF input every second until the ORG447X module starts by indicating a high on WAKEUP or generation of UART messages.

# 9.1. Starting the ORG447X series module

A pulse on the ON\_OFF input line when ORG447X FSM is ready and in startup-ready state, Hibernate state, standby state, will command the module to start.

ON\_OFF pulse requires a rising edge and high level that persists for at least 100  $\mu$ s in order to be detected. Resetting the ON\_OFF detector requires that ON\_OFF go to logic low at least 100  $\mu$ s.

- If the system is in Hibernate state, an ON\_OFF pulse will move to Full Power mode

- If the system is in Trickle Power Mode, an ON\_OFF pulse will move it to Full Power mode.

- If the system is in Push-To-Fix mode, an ON\_OFF pulse will initiate one Push-To-Fix cycle.

- If the system is already in Full Power mode, an ON\_OFF pulse will initiate orderly shutdown.

# **Fully Integrated GPS Modules**

| Symbol            | Parameter                            | Condition         | Min                            | Тур                            | Max                            | Units            |

|-------------------|--------------------------------------|-------------------|--------------------------------|--------------------------------|--------------------------------|------------------|

| f <sub>RTC</sub>  | RTC frequency                        | 25 <sup>0</sup> C | -20 ppm                        | 32768                          | +20 ppm                        | Hz               |

| t <sub>rtc</sub>  | RTC tick                             | 25 <sup>0</sup> C |                                | 30.5176                        |                                | μs               |

| $\Delta T_1$      | RTC startup time                     |                   |                                | 300                            |                                | ms               |

| $\Delta T_0$      | Power stabilization                  |                   | $6 \cdot t_{RTC} + \Delta T_1$ | $7 \cdot t_{RTC} + \Delta T_1$ | $8 \cdot t_{RTC} + \Delta T_1$ | μs               |

| $\Delta T_6$      | WAKEUP pulse                         | RTC running       |                                | 10                             |                                | t <sub>rtc</sub> |

| $\Delta T_{LOW}$  | ON_OFF low                           |                   | 3                              |                                |                                | t <sub>rtc</sub> |

| $\Delta T_{HIGH}$ | ON_OFF high                          |                   | 3                              |                                |                                | t <sub>rtc</sub> |

| $\Delta T_3$      | Startup sequencing                   | After ON_OFF      |                                | 1024                           |                                | t <sub>rtc</sub> |

| -                 | ON_OFF to WAKEUP high                | After ON_OFF      |                                | 6                              |                                | t <sub>rtc</sub> |

| $\Delta T_5$      | ON_OFF to ARM start                  | After ON_OFF      |                                | 2130                           |                                | t <sub>rtc</sub> |

| $\Delta T_7$      | Main power source start <sup>1</sup> | WAKEUP high       | 0                              | 30                             | 300                            | t <sub>rtc</sub> |

Table 9-1: Startup timing

Note:

1. When power provided through dual supply.

Low quescent current 1.8V source (LDO) for Hibernate state, and high efficiency 1.8V source (DC-DC) for Full Power state. The main power supply should be able to provide current for Full Power state within 1ms after WAKEUP is high.

# 9.2. Verifying the ORG447X series module has started

The ORG447X module WAKEUP output will go high indicating the internal processor has started. System activity indication depends upon the serial interface chosen. UART:

- With no flow control when active, the module will output NMEA messages at the 4800bps.

- With flow control nCTS must be released by host to allow the module to send messages. <sup>2</sup>C.

<u>I<sup>2</sup>C:</u>

- In Multi-Master mode with no bus contention the module will spontaneously send messages at the speed and message types selected.

- In Multi-Master mode with bus contention the module will send messages after the I<sup>2</sup>C bus contention resolution process allows it to send.

<u>SPI:</u>

- Since the module is SPI slave, there is no possible indication of system "ready" through SPI interface.

- The host must initiate SPI connection approximately one second after WAKEUP goes high.

# 9.3. Shutting down the ORG447X series module

Transferring the ORG447X module into Hibernate mode can be initiated in two ways:

- By a pulse on the ON\_OFF input when the ORG447X module in Full Power mode

- By serial messages in OSP (MID205) or NMEA (\$PSRF117)

The orderly shutdown may take anywhere from 10ms to 900ms to complete, depending upon operation in progress and messages pending, and hence is dependent upon serial interface speed and controls.

#### **Fully Integrated GPS Modules**

# **10.Software Functions**

The module supports NMEA-0183 ASCII protocol and One Socket Protocol (based on SiRF Binary Standard).

| Power On State                    |                   | Hibernate                                 |

|-----------------------------------|-------------------|-------------------------------------------|

| Default Interface <sup>1</sup>    |                   | SPI                                       |

| SPI data format                   |                   | NMEA                                      |

| UART data format                  |                   | NMEA                                      |

| UART settings                     |                   | 4,800 bps 8-N-1                           |

| I <sup>2</sup> C data format      |                   | NMEA                                      |

|                                   |                   | \$GPGGA @1 sec.                           |

|                                   |                   | \$GPGSA @ 1 sec.                          |

| NMEA Messages                     |                   | \$GPGSV @ 5 sec.                          |

|                                   |                   | \$GPRMC @ 1 sec.                          |

|                                   | SBAS <sup>2</sup> | OFF                                       |

|                                   | ABP <sup>2</sup>  | OFF                                       |

|                                   | Static Filter     | OFF                                       |

| Firmware features Track Smoothing |                   | OFF                                       |

|                                   | Internal DR       | OFF                                       |

|                                   | Low Power         | OFF                                       |

|                                   | Update rate       | 1Hz (configurable up to 5Hz) <sup>3</sup> |

Table 10-1: Operation defaults

Notes:

1. Without Pull-Up on nCTS or Pull-Down on nRTS.

2. Not available in modules with Standard firmware.

3. Future firmware.

#### **10.1. NMEA**

#### **NMEA Output Messages**

| Message                | Description                                                                           |

|------------------------|---------------------------------------------------------------------------------------|

| \$GPGGA                | Time, position and fix type data                                                      |

| \$GPGLL <sup>1</sup>   | Latitude, longitude, UTC time of position fix and status                              |

| \$GPGSA                | GPS receiver operating mode, satellites used in the position solution and DOP values  |

| \$GPGSV                | The number of GPS satellites in view, satellite ID, elevation, azimuth and SNR values |

| \$GPRMC                | Time, date, position, course and speed data                                           |

| \$GPVTG <sup>1</sup>   | Course and speed information relative to the ground                                   |

| \$PSRF150              | OK to send data to the module                                                         |

| \$PSRF155              | Extended Ephemeris Proprietary Message                                                |

| \$PSRF156,0x20         | ECLM ACK/NACK                                                                         |

| \$PSRF156,0x21         | ECLM EE Get Age response                                                              |

| \$PSRF156,0x22         | ECLM Get SGEE Age response                                                            |

| \$PSRF156,0x23         | ECLM Download Initiate Request                                                        |

| \$PSRF156,0x24         | ECLM Erase Storage File                                                               |

| \$PSRF156,0x25         | ECLM Update File Content                                                              |

| \$PSRF156,0x26         | ECLM Request File Content                                                             |

| \$PSRF160 <sup>2</sup> | Watchdog Timeout and Exception Condition                                              |

Note:

Table 10-2: NMEA protocol output messages

1. Not transmitted by default, can be enabled by \$PSRF103 command

# Fully Integrated GPS Modules

#### **NMEA Input Messages**

| Message ID     | Message                                          | Description                                        |  |  |

|----------------|--------------------------------------------------|----------------------------------------------------|--|--|

| \$PSRF100      | Set Serial Port Set UART parameters and protocol |                                                    |  |  |

| \$PSRF101      | Navigation Initialization                        | Parameters required for start using X/Y/Z          |  |  |

| \$PSRF103      | Query/Rate Control                               | Query standard NMEA message and/or set output rate |  |  |

| \$PSRF104      | LLA Navigation Initialization                    | Parameters required for start using Lat/Lon/Alt    |  |  |

| \$PSRF105      | Development Data On/Off                          | Development Data messages On/Off                   |  |  |

| \$PSRF106      | Select Datum                                     | Selection of an alternative map datum              |  |  |

| \$PSRF107      | Extended ephemeris propriet                      | ary message                                        |  |  |

| \$PSRF108      | Extended ephemeris propriet                      | ary message                                        |  |  |

| \$PSRF110      | Extended ephemeris debug                         |                                                    |  |  |

| \$PSRF114,0x16 | ECLM start download                              |                                                    |  |  |

| \$PSRF114,0x17 | ECLM file size                                   |                                                    |  |  |

| \$PSRF114,0x18 | ECLM packet data                                 |                                                    |  |  |

| \$PSRF114,0x19 | ECLM Get EE Age                                  |                                                    |  |  |

| \$PSRF114,0x1A | ECLM Get SGEE Age                                |                                                    |  |  |

| \$PSRF114,0x1B | ECLM Host File Content                           |                                                    |  |  |

| \$PSRF114,0x1C | ECLM Host ACK/NACK                               |                                                    |  |  |

| \$PSRF117      | System Turn Off                                  |                                                    |  |  |

| \$PSRF120      | Storage Configuration Setting                    |                                                    |  |  |

Table 10-3: NMEA protocol input messages

# 10.2. OSP (SiRF) Binary

# **OSP Binary Output Messages**

| MID (hex) | MID (dec) | Definition                    | Sub ID (hex) | Sub ID (dec) | Definition |

|-----------|-----------|-------------------------------|--------------|--------------|------------|

| 0 x 02    | 2         | Measured Navigation Data      |              |              |            |

| 0 x 03    | 3         | True Tracker Data             |              |              |            |

| 0 x 04    | 4         | Measured Tracking Data        |              |              |            |

| 0 x 06    | 6         | SW Version                    |              |              |            |

| 0 x 07    | 7         | Clock Status                  |              |              |            |

| 0 x 08    | 8         | 50 BPS Subframe Data          |              |              |            |

| 0 x 09    | 9         | Throughput                    |              |              |            |

| 0 x 0A    | 10        | Error ID                      |              |              |            |

| 0 x 0B    | 11        | Command Acknowledgement       |              |              |            |

| 0 x 0C    | 12        | Command No Acknowledgement    |              |              |            |

| 0 x 0D    | 13        | Visible List                  |              |              |            |

| 0 x 0E    | 14        | Almanac Data                  |              |              |            |

| 0 x 0F    | 15        | Ephemeris Data                |              |              |            |

| 0 x 10    | 16        | Test Mode 1                   |              |              |            |

| 0 x 12    | 18        | Ok To Send                    |              |              |            |

| 0 x 13    | 19        | Navigation Parameters         |              |              |            |

| 0 x 14    | 20        | Test Mode 2                   |              |              |            |

| 0 x 1B    | 27        | DGPS Status                   |              |              |            |

| 0 x 1C    | 28        | Nav. Lib. Measurement Data    |              |              |            |

| 0 x 1E    | 30        | Nav. Lib. SV State Data       |              |              |            |

| 0 x 1F    | 31        | Nav. Lib. Initialization Data |              |              |            |

| 0 x FF    | 255       | Development Data              |              |              |            |

Table 10-4: OSP binary output messages

# **Fully Integrated GPS Modules**

#### **OSP Binary Input Messages**

| MID (hex)        | MID (dec)   | Definition                       | Sub ID (hex)     | Sub ID (dec) | Definition                 |

|------------------|-------------|----------------------------------|------------------|--------------|----------------------------|

| 0 x 35           | 53          | Advanced Power Management        |                  |              |                            |

| 0 x 80           | 128         | Initialize Data Source           |                  |              |                            |

| 0 x 81           | 129         | Switch to NMEA Protocol          |                  |              |                            |

| 0 x 82           | 130         | Set Almanac (upload)             |                  |              |                            |

| 0 x 84           | 132         | Software Version (Poll)          |                  |              |                            |

| 0 x 84           | 132         | Set Main Serial Port             |                  |              |                            |

| 0 x 87           | 135         | Switch Protocol                  |                  |              |                            |

| 0 x 88           | 136         | Mode Control                     |                  |              |                            |

| 0 x 89           | 130         | DOP Mask                         |                  |              |                            |

| 0 x 8A           | 138         | MID_SET_DGPS_MODE                |                  |              |                            |

| 0 x 8B           | 130         | Elevation Mask                   |                  |              |                            |

| 0 x 8C           | 140         | Power Mask                       |                  |              |                            |

| 0 x 80           | 140         | Editing Residual                 |                  |              |                            |

| 0 x 8E           | 141         | Steady-State Detection           |                  |              |                            |

| 0 x 8E           | 142         | Static Navigation                |                  |              |                            |

| 0 x 81           | 143         | Poll Clock Status                |                  |              |                            |

| 0 x 90           | 144         | Poll Almanac                     |                  |              |                            |

| 0 x 93           | 140         | Poll Ephemeris                   |                  |              |                            |

| 0 x 95           | 147         | Set Ephemeris (upload)           |                  |              |                            |

| 0 x 95           | 149         | Switch Operating Mode            |                  |              |                            |

| 0 x 90           | 150         | Set Trickle Power Parameters     |                  |              |                            |

| 0 x 97           | 151         | Poll Navigation Parameters       |                  |              |                            |

| 0 x 98<br>0 x A5 | 165         | Set UART Configuration           |                  |              |                            |

| 0 x A5<br>0 x A6 | 165         | Set Message Rate                 |                  |              |                            |

| 0 x A0<br>0 x A7 | 166         | Low Power Acquisition Parameters |                  |              |                            |

| 0 x A7<br>0 x A8 | 167         | -                                |                  |              |                            |

| 0 x A8           | 168         | MID_POLL_CMD_PARAM<br>Set Datum  |                  |              |                            |

| 0 x A9           | 109         | Set SBAS Parameters              |                  |              |                            |

| U X AA           | 170         | Set SBAS Parameters              | 0 x 01           | 1            | Set DrNavInit              |

|                  |             |                                  | 0 x 01<br>0 x 02 | 1            |                            |

|                  |             |                                  |                  | 2            | Set DrNavMode              |

|                  |             |                                  | 0 x 03           |              | Set GyrFactCal             |

| 0 x AC           | 172         | MID_DrIn                         | 0 x 04           | 4 5          | Set DrSensParam            |

|                  |             |                                  | 0 x 05           | 5<br>6       | Poll DrValid               |

|                  |             |                                  | 0 x 06           |              | Poll GyrFactCal            |

|                  |             |                                  | 0 x 07           | 7            | Poll DrSensParam           |

| 0 11 4 5         | 475         | Cond Commented Statistics        | 0 x 13           | 19           | DR Debug Information       |

| 0 x AF           | 175         | Send Command String              | 014              | 20           | Detab Stars - Control      |

|                  |             |                                  | 0 x 14           | 20           | Patch Storage Control      |

|                  |             |                                  | 0 x 22           | 34           | Patch Memory Load Request  |

| 0 x B2           | 178         | SIRF_MSG_SSB_TRACKER_IC          | 0 x 26           | 38           | Patch Memory Exit Request  |

|                  |             |                                  | 0 x 28           | 40           | Patch Memory Start Request |

|                  |             |                                  | 0 x 90           | 144          | Patch Manager Prompt       |

|                  | <b>a</b> c- |                                  | 0 x 91           | 145          | Patch Manager Ack.         |

| 0 x CD           | 205         | Set Generic Software Control     | 0 x 10           | 16           | Software Commanded OFF     |

| 0 x D1           | 209         | MID_QUERY_REQ                    | -                |              |                            |

| 0 x D2           | 210         | MID_POS_REQ                      |                  |              |                            |

Table 10-5: OSP binary input messages

| MID (hex) | MID (dec) | Definition              | Sub ID (hex) | Sub ID (dec) | Definition               |

|-----------|-----------|-------------------------|--------------|--------------|--------------------------|

|           |           |                         | 0 x 01       | 1            | SET_IONO                 |

|           |           |                         | 0 x 02       | 2            | SET_EPH_CLOCK            |

|           |           |                         | 0 x 03       | 3            | SET_ALM                  |

|           |           |                         | 0 x 04       | 4            | SET_ACQ_ASSIST           |

| 0 x D3    | 211       | MID_SET_AIDING          | 0 x 05       | 5            | SET_RT_INTEG             |

|           |           |                         | 0 x 06       | 6            | SET_UTC_MODEL            |

|           |           |                         | 0 x 07       | 7            | SET_GPS_TOW_ASSIST       |

|           |           |                         | 0 x 08       | 8            | SET_AUX_NAV              |

|           |           |                         | 0 x 09       | 9            | SET_AIDING_AVAIL         |

|           |           |                         | 0 x 01       | 1            | EPH_REQ                  |

|           |           |                         | 0 x 02       | 2            | ALM_REQ                  |

|           |           |                         | 0 x 03       | 3            | B_EPH_REQ                |

| 0         | 242       |                         | 0 x 04       | 4            | TIME_FREQ_APPROX_POS_REQ |

| 0 x D4    | 212       | MID_STATUS_REQ          | 0 x 05       | 5            | CH_LOAD_REQ              |

|           |           |                         | 0 x 06       | 6            | CLIENT_STATUS_REQ        |

|           |           |                         | 0 x 07       | 7            | OSP_REV_REQ              |

|           |           |                         | 0 x 08       | 8            | SERIAL_SETTINGS_REQ      |

| 0         | 212       |                         | 0 x 01       | 1            | SESSION_OPEN_REQ         |

| 0 x D5    | 213       | MID_SESSION_CONTROL_REQ | 0 x 02       | 2            | SESSION_CLOSE_REQ        |

| 0 x D6    | 214       | MID_HW_CONFIG_RESP      |              |              |                          |

|           |           |                         | 0 x 01       | 1            | APPROX_MS_POS_RESP       |

|           |           |                         | 0 x 02       | 2            | TIME_TX_RESP             |

| 0xD7      | 215       |                         | 0 x 03       | 3            | FREQ_TX_RESP             |

|           |           |                         | 0 x 04       | 4            | SET_NBA_SF1_2_3          |

|           |           |                         | 0 x 05       | 5            | SET_NBA_SF4_5            |

| 0         | 210       |                         | 0 x 01       | 1            | ACK_NACK_ERROR           |

| 0xD8      | 216       | MID_MSG_ACK_IN          | 0 x 02       | 2            | REJECT                   |

| 0xD9      | 217       |                         | 0 x 01       | 1            | SENSOR_ON_OFF            |

|           |           |                         | 0 x 00       | 0            | FP_MODE_REQ              |

|           |           |                         | 0 x 01       | 1            | APM_REQ                  |

| 0xDA      | 218       | MID_PWR_MODE_REQ        | 0 x 02       | 2            | MPM_REQ                  |

|           |           |                         | 0 x 03       | 3            | TP_REQ                   |

|           |           |                         | 0 x 04       | 4            | PTF_REQ                  |

|           | 210       |                         | 0 x 01       | 1            | VCTCXO                   |

| 0xDB      | 219       | MID_HW_CTRL_IN          | 0 x 02       | 2            | ON_OFF_SIG_CONFIG        |

|           |           |                         | 0 x 01       | 1            | CONFIG                   |

|           |           |                         | 0 x 02       | 2            | EVENT_REG                |

| 0xDC      | 220       | MID_CW_CONTROLLER_REQ   | 0 x 03       | 3            | COMMAND_SCAN             |

|           |           |                         | 0 x 04       | 4            | CUSTOM_MON_CONFIG        |

|           |           |                         | 0 x 05       | 5            | FFT_NOTCH_SETUP          |

| 0, 51     | 225       |                         | 0 x 06       | 6            | STATISTICS               |

| 0xE1      | 225       | MID_SiRFOutput          | 0 x 07       | 7            | Statistics with Aiding   |

Table 10-5: OSP binary input messages

| MID (hex) | MID (dec) | Definition                 | Sub ID (hex) | Sub ID (dec)        | Definition             |                      |

|-----------|-----------|----------------------------|--------------|---------------------|------------------------|----------------------|

|           |           |                            | 0 x 01       | 1                   | SSB_EE_SEA_PROVIDE_EPH |                      |